# Hardware Reference

## VME-4145

4-Channel 16-bit Arbitrary Waveform Generator Board with Autocalibration First Edition

#### Part No: 500-024145-000 REV. A

© GE Fanuc Intelligent Platforms Inc 2008

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise without the prior written permission of GE Fanuc Intelligent Platforms Inc.

This document contains Confidential/Proprietary Information belonging to GE Fanuc Intelligent Platforms Inc.

#### **Document History**

Hardware Reference Manual Document Number: 500-024145-000 REV. A June 2, 2008

## **Table of Contents**

| List of Figures                              |    |

|----------------------------------------------|----|

| List of Tables                               |    |

| Overview                                     |    |

| 1 • Configuration and Installation.          |    |

| 1.1 Unpacking Procedures.                    |    |

| 1.2 Handling Precaution.                     |    |

| 1.3 Hardware Setup.                          |    |

| 1.4 Installation.                            |    |

| 1.4.1 Before Applying Power: Checklist       |    |

| 1.5 Operational Configuration.               |    |

| 1.5.1 VME Access                             |    |

| 1.5.2 Base Address Jumpers                   |    |

| 1.5.3 Two-Channel Mezzanine Board            |    |

| 1.5.4 Test Points                            | 27 |

| 1.5.5 Potentiometers                         | 27 |

| 1.5.6 Fuses                                  | 27 |

| 1.5.7 Headers                                | 27 |

| 1.6 Calibration                              | 27 |

| 1.6.1 Test Equipment Required:               |    |

| 1.6.2 +10.0VDC Reference Voltage Calibration | 28 |

| 1.6.3 +5.0VDC Reference Voltage Calibration  | 28 |

| 1.6.4 +2.5VDC Reference Voltage Calibration  | 28 |

| 2 • Theory of Operation                      |    |

| 2.1 Géneral Operation.                       |    |

| 2.1.1 VME-4145 Onboard RAM                   |    |

| 2.1.2 Output Range                           |    |

| 2.1.3 Data Engine Registers                  |    |

| 2.1.4 Loading the Waveform Data Table        |    |

| 2.2 Modes of Operation.                      | 33 |

| 2.2.1 Continuous Modes Types I and II        |    |

| 2.2.2 Single Cycle Mode                      |    |

| 2.2.3 Continuous Burst Mode                  |    |

| 2.3 Idle Timer                               |    |

| 2.4 Cycle Counter.                           |    |

| 2.4.1 Examples of Setting Up Modes           |    |

| 2.5 Sample Clock and Trigger.                |    |

| 2.5.1 Internal Sample Clock                  |    |

| 2.5.2 External Sample Clock                  |    |

| 2.5.3 External Trigger                       |    |

| 2.6 Hardware States.                         |    |

| 2.7 VME Interface.                           |    |

|                                              |    |

| 2.8 Commands                                         |    |

|------------------------------------------------------|----|

| 2.9 Calibration.                                     |    |

| 2.10 Digital Signal Processor (DSP)                  |    |

| 2.11 EPROM                                           |    |

| 2.12 E2PROM                                          |    |

| 2.13 Control Logic.                                  |    |

| 2.14 Analog Circuitry.                               | 41 |

| 2.14.1 Digital-to-Analog Converter (DAC)             |    |

| 2.14.2 Analog-to-Digital Converter (ADC)             |    |

| 2.14.3 Analog Output Filtering (Optional)            |    |

| 2.14.4 Self-Test                                     |    |

| 2.14.5 System Reset                                  |    |

| 2.14.6 Transfer Function                             |    |

| 2.14.7 Output Impedance and Drive                    |    |

| 2.14.8 Output Short Circuit Protection               |    |

| 2.14.9 Field Disconnect                              |    |

| 2.14.10 Sync Pulse Output                            |    |

| 2.14.11 Front Panel Status LED                       |    |

| 2.14.12 Front Panel Reference Voltage Access         |    |

| 2.14.13 Front Panel Clock Connection                 |    |

| 2.14.14 Front Panel Signal Buffers                   |    |

| 3 • Programming                                      |    |

| 3.1 Getting Started                                  |    |

| 3.1.1 Sequence of Initialization                     |    |

| 3.1.2 Guidelines on Defining Waveforms               |    |

| 3.2 VME Memory Map                                   |    |

| 3.2.1 VME Data Memory Map Overview                   |    |

| 3.3 Register Definitions                             |    |

| 3.3.1 Board ID Register (BID)                        |    |

| 3.3.2 DAC Channel Pointer (CHN)                      |    |

| 3.3.3 VME Command Register (VCR)                     |    |

| 3.3.4 Command Data Registers (CDRs)                  |    |

| 3.3.5 Command Response Register (CRR)                |    |

| 3.3.6 General Configuration Register (GCR)           |    |

| 3.3.7 Self-Test Status Register (SSR)                |    |

| 3.3.8 Software Reset (RST)                           |    |

| 3.3.9 Firmware Revision Register (FRR)               |    |

| 3.3.10 Channel Status Register (CSR0 - CSR3)         |    |

| 3.3.11 Channel Status Register Bit Definition        |    |

| 3.3.12 Channel Configuration Registers (CCR0 - CCR3) | 61 |

| 3.3.13 Internal Time Base Registers                  | 62 |

| 3.3.14 Idle Time Registers                           |    |

| 3.3.15 Starting Address Pointer Registers            | 65 |

| 3.3.16 Ending Address Pointer Registers              |    |

|     | 3.3.17 Clock MUX Register                                                   | .65 |

|-----|-----------------------------------------------------------------------------|-----|

|     | 3.3.18 Self-Test Status Registers (STSO - STS3)                             | .66 |

|     | 3.3.19 DAC Calibration Status Registers (CAL0-CAL3)                         | .68 |

|     | 3.3.20 General Test Status Register (GTS)                                   | .69 |

|     | 3.3.21 ADC Calibration Status Register (ADCS)                               | .69 |

|     | 3.3.22 DAC Gain Coefficient Registers for Channel 0 (GCOEF0)                | .70 |

|     | 3.3.23 DAC Offset Coefficient Registers for Channel 0 (OCOEF0)              | .70 |

|     | 3.3.24 DAC Gain Coefficient Registers for Channel 1 (GCOEF1)                | .70 |

|     | 3.3.25 DAC Offset Coefficient Registers for Channel 1 (OCOEF1)              | .70 |

|     | 3.3.26 DAC Gain Coefficient Registers for Channel 2 (GCOEF2)                | .70 |

|     | 3.3.27 DAC Offset Coefficient Registers for Channel 2 (OCOEF2)              | .71 |

|     | 3.3.28 DAC Gain Coefficient Registers for Channel 3 (GCOEF3)                | .71 |

|     | 3.3.29 DAC Offset Coefficient Registers for Channel 3 (OCOEF3)              | .71 |

|     | 3.3.30 ADC Gain Coefficient Registers (ADCGCOEF)                            | .71 |

|     | 3.3.31 ADC Offset Coefficient Registers (ADCOCOEF)                          | .71 |

|     | 3.3.32 DAC Gain Coefficient Registers (GCOEF)                               | .72 |

|     | 3.3.33 DAC Offset Coefficient Registers (OCOEF1)                            | .72 |

|     | 3.3.34 DAC Calibration Raw Data Storage Area [64] (DACRAWO)                 | .72 |

|     | 3.3.35 DAC Calibration Raw Data Storage Area [64] (DACRAW1)                 |     |

|     | 3.3.36 DAC Calibration Raw Data Storage Area [64] (DACRAW2)                 | .73 |

|     | 3.3.37 DAC Calibration Raw Data Storage Area [64] (DACRAW3)                 | .73 |

|     | 3.3.38 DAC Calibration Real Data Storage Area [64] (DACREALO)               | .73 |

|     | 3.3.39 DAC Calibration Real Data Storage Area [64] (DACREAL1)               | .74 |

|     | 3.3.40 DAC Calibration Real Data Storage Area [64] (DACREAL2)               | .74 |

|     | 3.3.41 DAC Calibration Real Data Storage Area [64] (DACREAL3)               | .74 |

|     | 3.3.42 ADC Calibration Raw Data Storage Area [64] (ADCRAW0)                 | .75 |

|     | 3.3.43 ADC Calibration Raw Data Storage Area [64] (ADCRAW1)                 | .75 |

|     | 3.3.44 ADC Calibration Raw Data Storage Area [64] (ADCRAW2)                 | .75 |

|     | 3.3.45 ADC Calibration Raw Data Storage Area [64] (ADCRAW3)                 | .75 |

|     | 3.3.46 ADC Calibration Real Data Storage Area [64] (ADCREAL0)               | .76 |

|     | 3.3.47 ADC Calibration Real Data Storage Area [64] (ADCREAL1)               | .76 |

|     | 3.3.48 ADC Calibration Real Data Storage Area [64] (ADCREAL2)               | .76 |

|     | 3.3.49 ADC Calibration Real Data Storage Area [64] (ADCREAL3)               | .76 |

| 3.4 | Segmented Waveform Programming.                                             | .77 |

| 3.5 | VME-4145 Commands.                                                          | .79 |

|     | 3.5.1 Command: Null                                                         | .80 |

|     | 3.5.2 Command: Load General Configuration                                   | .80 |

|     | 3.5.3 Command: Load Channel Configuration                                   | .80 |

|     | 3.5.4 Command: Load Idle Time                                               | .81 |

|     | 3.5.5 Command: Initialize Channel Engine or Halt Wave form Generation       | .81 |

|     | 3.5.6 Command: Load Full Waveform Table without Gain/Offset Autocalibration | .82 |

|     | 3.5.7 Command: Software Trigger Channel Command                             | .83 |

|     | 3.5.8 Command: Load Sample Rate                                             | .83 |

|     | 3.5.9 Command: Generate Automatic Square Wave                               | .83 |

| 3.5.10 Command: Ping DSP                                                  |    |

|---------------------------------------------------------------------------|----|

| 3.5.11 Command: Built-In-Test Command                                     |    |

| 3.5.12 Command: Report EPLD Engine Status Command                         |    |

| 3.5.13 Command: Load Repeat Count                                         |    |

| 3.5.14 Command: Load Starting and Ending Address Pointers                 |    |

| 3.5.15 Command: Load Clock Multiplexer                                    |    |

| 3.5.16 Command: Enable Segmentation                                       |    |

| 3.5.17 Command: Disable Segmentation                                      |    |

| 3.5.18 Command: Report DSP Hardware Status                                |    |

| 3.5.19 Command: Software Reset                                            |    |

| 3.5.20 Command: Calibrate Channels                                        |    |

| 3.5.21 Command: Load Full Waveform Table with Gain/Offset Autocalibration |    |

| 3.5.22 Command: Download CAL Data from E2PROM to VME RAM                  |    |

| 3.5.23 Command: Upload CAL Data from VME RAM to E2PROM                    |    |

| 3.5.24 Command: DSP/ADC/DAC Self-Test                                     |    |

| Maintenance                                                               |    |

| A • Appendix A: Sample Codes                                              | 94 |

A•

## List of Figures

| Figure 1-1 VME-4145 Jumper and Test Point Locations                            |    |

|--------------------------------------------------------------------------------|----|

| Figure 1-2 Jumper Locations and Test Points on the Two-Channel Mezzanine Board |    |

| Figure 1-3 VME-4145 Front Panel                                                |    |

| Figure 1-4 VME Memory Mode Configuration                                       |    |

| Figure 1-5 VME Access Mode Configuration                                       |    |

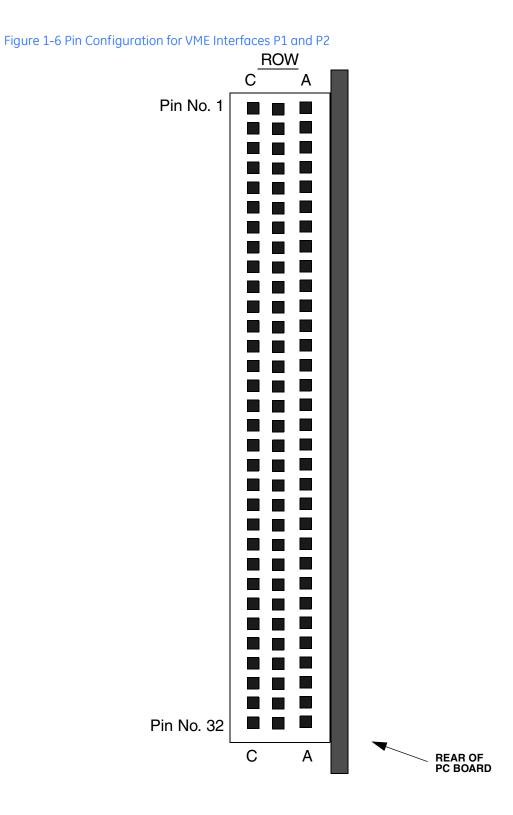

| Figure 1-6 Pin Configuration for VME Interfaces P1 and P2                      |    |

| Figure 1-7 Base Address Jumper Configuration                                   |    |

| Figure 1-8 Example of Base Address Jumper Usage                                |    |

| Figure 2-1 VME-4145 Functional Block Diagram                                   |    |

| Figure 2-2 VME-4145 RAM Structure                                              |    |

| Figure 2-3 Example of the Burst Mode Type I                                    |    |

| Figure 2-4 Sample Clock                                                        |    |

| Figure 2-5 External Trigger                                                    |    |

| Figure 3-1 EPLD State Machine Diagram                                          | 60 |

## List of Tables

| Table 1-1 Main Board Jumper Descriptions                           |

|--------------------------------------------------------------------|

| Table 1-2 Jumper Description for Mezzanine Board    21             |

| Table 1-3 Test Point Descriptions                                  |

| Table 1-4 Potentiometer Descriptions                               |

| Table 2-1 Bipolar and Unipolar Voltage Ranges32                    |

| Table 2-2 Example Settings: Modes                                  |

| Table 2-3 Filters Available for the VME-4145                       |

| Table 3-1 VME Memory Map.   48                                     |

| Table 3-2 VME Data Memory Map Overview                             |

| Table 3-3 Board ID Register Bit Map                                |

| Table 3-4 DAC Channel Pointer Register Bit Map       54            |

| Table 3-5 Two-Bit Binary                                           |

| Table 3-6 VME Command Register Bit Map       55                    |

| Table 3-7 Command Data Register Descriptions                       |

| Table 3-8 Command Response Register Bit Map       56               |

| Table 3-9 Command Response Register Code Identification       56   |

| Table 3-10 General Configuration Register Bit Map    57            |

| Table 3-11 Self-Test Status Register Bit Map       58              |

| Table 3-12 Firmware Revision Register Bit Map       58             |

| Table 3-13 Channel Status Register Bit Map                         |

| Table 3-14 Engine State Machine Code Identification                |

| Table 3-15 Channel Configuration Registers Bit Map       61        |

| Table 3-16 Analog Output Range Settings      61                    |

| Table 3-17 Trigger Selections                                      |

| Table 3-18 Internal Time Base Register Bit Map       62            |

| Table 3-19 Idle Time Register Bit Map64                            |

| Table 3-20 Starting Address Pointer Register Bit Map65             |

| Table 3-21 Ending Address Pointer Register Bit Map       65        |

| Table 3-22 Clock MUX Register Bit Map65                            |

| Table 3-23 Clock MUX Code Identification                           |

| Table 3-24 Common Clock Code Identification                        |

| Table 3-25 Hardware Failure Codes for Self-Test Status       67    |

| Table 3-26 DAC Hardware Failure Codes for Calibration Status       |

| Table 3-27 Hardware Failure Codes for General Test Status       69 |

| Table 3-28 ADC Hardware Failure Codes for Calibration Status       |

| Table 3-29 Segmentation Pointer Descriptions       77              |

| Table 3-30 Index of Commands on the VME-4145                       |

| Table 3-31 Built-in-Test Command Reference Values                  |

| Table 3-32 DSP Output Data Format                                  |

| Table 3-33 ADC Attenuator Input Port Definitions                   |

| Table 3-34 DSP Hardware Status Register Bit Map  |  |

|--------------------------------------------------|--|

| Table 3-35 DSP Hardware Control Register Bit Map |  |

## Overview

GE Fanuc Intelligent Platforms' VME-4145 is an Analog Output board that provides four high-quality analog output channels with 16-bit resolution. Each output has a dedicated Digital-to-Analog Converter (DAC), and can source or sink 10 mA ±10 V. Each channel has a dedicated 64 Kword waveform buffer. The buffer is scanned at a user-programmable rate. The buffer data is fed to its dedicated DAC. Loading appropriate data will cause the DAC's output to generate an arbitrary waveform. Each buffer may be segmented to provide independent subwaveforms. This segmentation allows switching between multiple output waveforms at high speeds. The analog outputs can be independently disconnected from the field wiring for offline testing.

Autocalibration is initiated by a VME software command. An onboard Digital Signal Processor (DSP) and a 20-bit Analog-to-Digital Converter (ADC) are used to calibrate the offsets and gains of the DACs. During calibration, a table of offset and gain coefficients are compiled and stored in RAM. There are entries for offset and gain corresponding to each of the four channels configured in each of the five output voltage ranges.

The unit is designed to download an arbitrary waveform and then replay it. Any arbitrary waveform may be programmed. The standard square, sine, triangle, and ramp are but a small sampling of the types of waveforms that may be generated. It is the user's responsibility to generate a table of hexadecimal data corresponding to the voltages required for their waveform. The appendix has several examples of C code programs which illustrate programming of the board. The VME-4145 contains a built-in square-wave generator command. This automatic waveform is useful to quickly determine proper operation of the unit. The user's software must download this waveform table from the VME host into the board's waveform buffer RAM memory. There are five separate 64 K x 16 RAM memories. The first is a dual-port RAM and is accessible by the VME host processor and onboard DSP processor. The user downloads an arbitrary waveform table into this common memory. During this download period, all four channels may be "playing-out" the information previously stored in their four dedicated RAM memories. Once the user completes downloading from the VME into the common RAM, the user instructs the DSP to move the common buffer data to one of the four output channels. At this point, the DSP must take the desired channel offline to update its RAM memory with the new waveform stored in the common memory. This block movement takes a minimum of 9.2 µs per sample; the larger the waveform table size, the longer it will take. During this block movement, the DSP will apply gain and offset corrections to the user's data if calibration is required.

To enable the VME-4145 to change from one waveform to another waveform in real time, the unit supports segmentation. The user may segment the 64 K waveform space into multiple smaller waveforms. A maximum of 64 unique waveforms, each up to 1,024 words in length, may be programmed. In real time, the user may switch between any one of these 64 waveforms or program an automatic seamless sequencing of any number of these. Each waveform is generated start to finish and then the next is seamlessly started. A link list software approach is used to program the sequencing of segments in real time by the host processor. All of the waveforms must be preloaded before waveform generation begins. The VME-4145 supports an external trigger input. This is used to control the VME-4145 externally. A trigger event will cause the VME-4145 to start playback of a waveform. Before the waveform has completed one cycle through the table, the user may retrigger the unit. This will restart the waveform output from the beginning. This feature allows the unit to be synchronized to some external condition.

The VME-4145 supports sweeping of the output frequency. The board's internal sample rate clock (one of four) may be changed in real time while a waveform is being generated. This feature requires real-time VME host control interaction. The host may instruct the DSP to change the internal sample rate clock at any time. The board also supports external input of the sample clock. The external source may also sweep its frequency. Finally, the output clock's static logic (one or zero) state may be programmed by the host for extremely long output update rates. Channel zero's sample clock may also be used as a common clock to synchronize any or all of the remaining channels to the same rate. The fastest rate from one sample to the next is 400 ns, equivalent to 2.5 million samples per second.

#### **Features**

The VME-4145 features the following:

- Four-channel analog waveform generator

- Autocalibration of all channels to a single reference

- Continuous burst, single burst, or burst/idle/burst modes

- One 16-bit DAC per output

- Programmable sample clock for each channel, internal or external

- Up to 2.5 million samples/second

- External clock and trigger input per channel

- Variable length (up to 65,536 word) waveform buffer per channel

- Buffer segmentation for multiple waveforms in memory

- Unipolar 5 and 10 V ranges, Bipolar 2.5, 5, and 10 V ranges

- 10 mA output drive current per channel

- 1.5 Ω output impedance per channel

- Deglitched DAC outputs with optional 4-pole low pass filtering

- External SYNC output (per channel)

- Onboard DSP and 20-bit Analog-to-Digital Converter for automatic calibration and diagnostic self-test

- Field wiring disconnect for offline self-test diagnostics

- Front panel reference voltage(s) access

- Programmable SYNC pulse polarity

- Trigger input: Level HI/LO or rising/falling edge per channel.

#### Organization

This manual is composed of the following chapters and appendix:

*Overview* provides a general description of the VME-4145 and General Safety terms and symbols.

*Chapter 1 Configuration and Installation* describes unpacking, inspection, hardware jumper settings, connector definitions, installation, and system setup of the VME-4145.

*Chapter 2 Theroy of Operation* describes functionality, hardware settings, connector definitions, and operation of the VME-4145.

*Chapter 3 Programming* describes the sequence of initialization, defining waveforms and commands for wave generation, along with the coefficient registers for channels.

*Maintenance* provides GE Fanuc Intelligent Platforms' contact information relative to the care and maintenance of the unit.

Appendix A Sample Codes illustrates and defines the code samples.

#### References

For a detailed description and specification of the VMEbus, please refer to:

VMEbus Specification Rev. C. and the VMEbus Handbook

VMEbus International Trade Assoc. (VITA) 7825 East Gelding Dr. Suite 104 Scottsdale, AZ 85260 (602) 951-8866 (602) 951-0720 (FAX) www.vita.com

## Safety Summary

|                                                 | The following general safety precautions must be observed during all phases of<br>the operation, service and repair of this product. Failure to comply with these<br>precautions or with specific warnings elsewhere in this manual violates safety<br>standards of design, manufacture and intended use of this product.                                                                                                     |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 | GE Fanuc Intelligent Platforms assumes no liability for the customer's failure to comply with these requirements.                                                                                                                                                                                                                                                                                                             |

| Ground the<br>System                            | To minimize shock hazard, the chassis and system cabinet must be connected to<br>an electrical ground. A three-conductor AC power cable should be used. The<br>power cable must either be plugged into an approved three-contact electrical<br>outlet or used with a three-contact to two-contact adapter with the grounding<br>wire (green) firmly connected to an electrical ground (safety ground) at the power<br>outlet. |

| Do Not Operate in<br>an Explosive<br>Atmosphere | Do not operate the system in the presence of flammable gases or fumes. Operation of any electrical system in such an environment constitutes a definite safety hazard.                                                                                                                                                                                                                                                        |

| Keep Away from<br>Live Circuits                 | Operating personnel must not remove product covers. Component replacement<br>and internal adjustments must be made by qualified maintenance personnel. Do<br>not replace components with power cable connected. Under certain conditions,<br>dangerous voltages may exist even with the power cable removed. To avoid<br>injuries, always disconnect power and discharge circuits before touching them.                       |

| Do Not Service or<br>Adjust Alone               | Do not attempt internal service or adjustment unless another person capable of rendering first aid and resuscitation is present.                                                                                                                                                                                                                                                                                              |

| Do Not Substitute<br>Parts or Modify<br>System  | Because of the danger of introducing additional hazards, do not install substitute<br>parts or perform any unauthorized modification to the product. Return the<br>product to GE Fanuc Intelligent Platforms for service and repair to ensure that<br>safety features are maintained.                                                                                                                                         |

| Dangerous<br>Procedure<br>Warnings              | Warnings, such as the example below, precede only potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.                                                                                                                                                                                                                                                           |

|                                                 | A WARNING                                                                                                                                                                                                                                                                                                                                                                                                                     |

Dangerous voltages, capable of causing death, are present in this system. Use extreme caution when handling, testing and adjusting.

#### WARNING

WARNING denotes a hazard. It calls attention to a procedure, practice, or condition, which, if not correctly performed or adhered to, could result in injury or death to personnel.

## CAUTION

CAUTION denotes a hazard. It calls attention to an operating procedure, practice, or condition, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the system.

NOTE

NOTE denotes important information. It calls attention to a procedure, practice, or condition which is essential to highlight.

Tip denotes a bit of expert information.

## **1** • Configuration and Installation

This chapter describes the hardware jumper settings, connector descriptions, installation, system setup and configuration of the VME-4145.

#### **1.1 Unpacking Procedures**

Any precautions found in the shipping container should be observed. All items should be carefully unpacked and thoroughly inspected for damage that might have occurred during shipment. The board(s) should be checked for broken components, damaged printed circuit board(s), heat damage and other visible contamination. All claims arising from shipping damage should be filed with the carrier and a complete report sent to GE Fanuc Intelligent Platforms Customer Care.

Some of the components assembled may be sensitive to electrostatic discharge and damage may occur on boards that are subjected to a high energy electrostatic field. When the board is placed on a bench for configuring, etc., it is suggested that conductive material be inserted under the board to provide a conductive shunt. Unused boards should be stored in the same protective boxes in which they were shipped.

#### **1.2 Handling Precaution**

Electronic assemblies use devices that are sensitive to static discharge. Observe anti-static procedures when handling these boards. All products should be in an anti-static plastic bag or conductive foam for storage or shipment. Work at an approved anti-static workstation when unpacking boards.

#### **1.3 Hardware Setup**

The VME-4145 is factory populated with user-specified options as part of the VME-4145 ordering information. Contact customer care to receive a Return Material Authorization (RMA). RMAs are available at rma@gefanuc.com

GE Fanuc Intelligent Platforms Customer Care is available at: 1-800-GEFANUC

(1-800-240-7782), 1-780-401-7700 or E-mail us at support.embeddedsystems@gefanuc.com

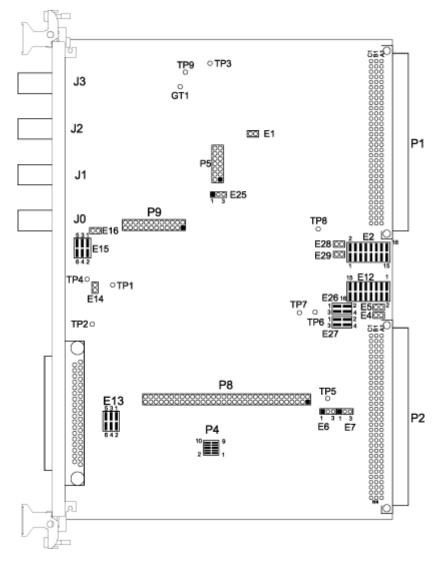

The VME-4145 is tested for system operation and shipped with factory-installed header jumpers. The physical location of the jumpers and connectors for the VME-4145 are illustrated in Figure 1-1.

All jumpers marked *User Configurable* in the following tables may be changed or modified by the user. All jumpers marked *Factory Configured* should not be modified by the user.

Care must be taken when making jumper modifications to ensure against improper settings or connections. Improper settings may result in damage to the unit.

CAUTION Modifying any jumper not marked *User Configurable* will void the Warranty and may damage the unit. The default jumper condition of the VME-4145 is expressed in Table 1-1.

#### **1.4 Installation**

CAUTION Do not install or remove the boards while power is applied.

De-energize the equipment and insert the board into an appropriate slot of the chassis. While ensuring that the board is properly aligned and oriented in the supporting card guides, slide the board smoothly forward against the mating connector until firmly seated.

#### 1.4.1 Before Applying Power: Checklist

Before installing the board in a VME system, check the following items to ensure that the board is ready for the intended application.

- 1. Verify that the sections pertaining to programming and configuration, Chapter 1 Configuration and Installation and Chapter 3 Programming, have been reviewed and applied to system requirements.\_\_\_\_\_

- 2. Review Table 1-1 on page 19 and Table 1-2 on page 21 to verify that all jumpers are configured correctly for the application.

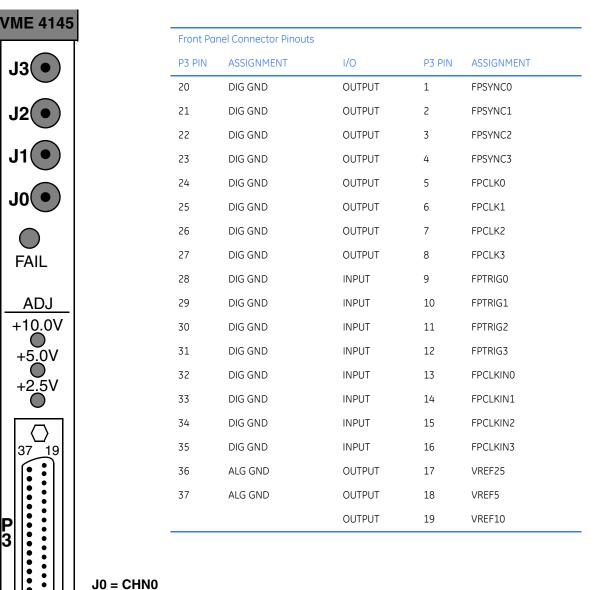

- 3. Verify that the I/O cables are properly terminated for the input/output connectors. Refer to Figure 1-3 for connector descriptions. \_\_\_\_\_

- 4. Ensure that all system cable connections are correct.

- 5. Calibration has been performed at the factory. If recalibration should be required, refer to "Calibration" on page 27. \_\_\_\_\_

After the checklist above has been completed, the board can be installed in a VME system. This board can be installed in any slot position, except slot one which is reserved for the system controller.

#### **1.5 Operational Configuration**

Control of the VME-4145 board address and I/O access mode are determined by field configurable, onboard jumpers. This section describes the use of those jumpers, and their effects on board performance. The locations and functions of all VME-4145 jumpers are shown in Figure 1-1 and Figure 1-2. For jumper settings refer to the Table 1-1 on page 19 and Table 1-2 on page 21.

Figure 1-1 VME-4145 Jumper and Test Point Locations

| Table 1-1 | . Main Board | Jumper | Descriptions |

|-----------|--------------|--------|--------------|

|-----------|--------------|--------|--------------|

| Jumper | Pins         | Description                                                                  | Factory Default |

|--------|--------------|------------------------------------------------------------------------------|-----------------|

| E1     | UIOC Control |                                                                              |                 |

|        | 1-2          | Jumper Off - Logic 1 - No UIOC Control<br>Jumper On - Logic 0 - UIOC Control | Omitted         |

| E4     | 1-2          | Install for External -15 VDC Power Supply                                    | Omitted         |

| E5     | 1-2          | Install for External +15 VDC Power Supply                                    | Omitted         |

| E6     | 1-2          | Local -15 V Power                                                            | Installed       |

|        | 2-3          | Remote -15 V Power                                                           | Omitted         |

| E7     | 1-2          | Local +15 V Power                                                            | Installed       |

|        | 2-3          | Remote +15 V Power                                                           | Omitted         |

| Jumper                   | Pins                              | Description                                                                                                                                                                  | Factory Default |

|--------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| E13                      | Channel 0 Output Offset S         | elect                                                                                                                                                                        |                 |

| See Note 1<br>See Note 2 | 1-2                               | Install to Use Channel 1 DAC to Offset DC<br>Zero Point of Channel 0 Output<br>DO NOT INSTALL 3-4 OR 5-6 WITH THIS<br>OPTION, IT WILL SHORT OUT THE<br>CHANNEL 1 DAC OUTPUT. | Omitted         |

|                          | 3-4                               | Install to Use J0 BNC's Ground for Remote<br>Ground Sense                                                                                                                    | Installed       |

|                          | 5-6                               | Install to Disable This Offset/Remote<br>Ground Sense Feature                                                                                                                | Installed       |

| E14                      | 1-2                               | Jumper On - Channel 0 Bipolar Output<br>Range<br>Jumper Off - Channel 0 Unipolar Output<br>Range                                                                             | Installed       |

| E15                      | Channel 1 Output Offset S         | elect                                                                                                                                                                        |                 |

|                          | 1-2                               | NOT USED                                                                                                                                                                     | Omitted         |

|                          | 3-4                               | Install to Use J1 BNC's Ground for Remote<br>Ground Sense                                                                                                                    | Installed       |

|                          | 5-6                               | Install to Disable This Remote Ground Sense<br>Feature                                                                                                                       | Installed       |

| E16                      | 1-2                               | Jumper On - Channel 1 Bipolar Output<br>Range<br>Jumper Off - Channel 1 Unipolar Output<br>Range                                                                             | Installed       |

| E25                      | ADC Clock Source                  |                                                                                                                                                                              |                 |

|                          | 1-2                               | DSP                                                                                                                                                                          | Omitted         |

|                          | 2-3                               | Serial                                                                                                                                                                       | Installed       |

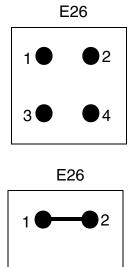

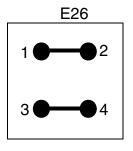

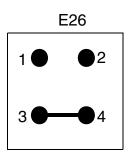

| E26<br>See Note 3        | 1-2 or<br>1-2 and 3-4             | Supervisory and Nonprivileged                                                                                                                                                | Installed       |

|                          | 3-4 Only                          | Nonprivileged                                                                                                                                                                | Installed       |

|                          | None                              | Supervisory                                                                                                                                                                  |                 |

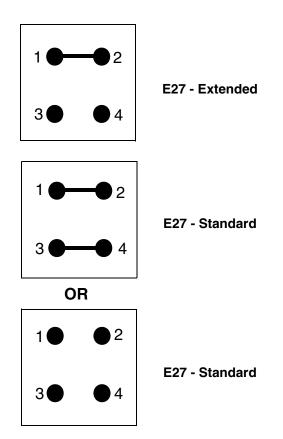

| E27<br>See Note 7        | 1-2                               | Extended Addressing                                                                                                                                                          | Installed       |

| See Note 3               | 1-2 and 3-4 or None<br>See Note 3 | Standard Addressing                                                                                                                                                          | Omitted         |

| E28                      | DSP Status Register Bit D1        | .2, Undefined Function                                                                                                                                                       |                 |

|                          | 1-2                               | Jumper On - Logic 0<br>Jumper Off - Logic 1                                                                                                                                  | Omitted         |

| E29                      | DSP Status Register Bit D1        | 1, Factory Only                                                                                                                                                              |                 |

| See Note 3               | 1-2                               | Jumper On - Logic 0<br>Jumper Off - Logic 1                                                                                                                                  | Omitted         |

#### Table 1-1 Main Board Jumper Descriptions (Continued)

Note 1 - This offset is electronically limited to ±5.6VDC limits due to headroom of the output OP Amps.

**Note 2** - If the user wishes the output connectors J0-J3 outer ground to be tied to the VME-4145's local analog ground, the user may install jumpers on both 3-4 and 5-6 pins.

**Note 3** - The mezzanine board must be removed to modify this option. The options are located on the main board. It is advisable to have someone skilled in electronics remove this option board to prevent damage to the unit. Carefully grip firmly on all four corners of the mezzanine board to remove it from P8 and P9. Make sure all pins of the mezzanine's P1 and P2 are aligned correctly before reinstalling the unit.

This document contains Confidential/Proprietary Information belonging to GE Fanuc Intelligent Platforms Inc.

#### Table 1-2 Jumper Description for Mezzanine Board

| E17<br>See Note 4 | Channel 2 Output Offset Select |                                                                                                                                                                            |           |

|-------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                   | 1-2                            | Install for Channel 3 DAC to Offset DC Zero<br>Point of Channel 2 Output.<br>DO NOT INSTALL 3-4 OR 5-6 WITH THIS<br>OPTION, IT WILL SHORT OUT THE CHANNEL<br>3 DAC OUTPUT! | Omitted   |

|                   | 3-4                            | Install to Use J2 BNC's Ground for Remote<br>Ground Sense                                                                                                                  | Installed |

|                   | 5-6                            | Install to Disable This Offset/Remote Ground Sense Feature                                                                                                                 | Installed |

| E18<br>See Note 4 | 1-2                            | Jumper On - Channel 2 Bipolar Output<br>Range Select<br>Jumper Off - Unipolar Output Range Select                                                                          | Installed |

| E19<br>See Note ( | Channel 3 Output Offset Select |                                                                                                                                                                            |           |

| See Note 4        | 1-2                            | Not Used                                                                                                                                                                   | Omitted   |

|                   | 3-4                            | Install to Use J3 BNC's Ground for Remote Ground Sense                                                                                                                     | Installed |

|                   | 5-6                            | Install to Disable This Remote Ground Sense<br>Feature                                                                                                                     | Installed |

| E14<br>See Note 4 | 1-2                            | Jumper On - Channel 3 Bipolar Output<br>Range Select<br>Jumper Off - Unipolar Output Range Select                                                                          | Installed |

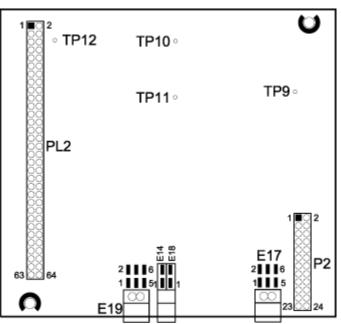

**Note 4** - The mezzanine board must be removed to modify this option. The options are located on the mezzanine board. It is advisable to have someone skilled in electronics remove this option board to prevent damage to the unit. Carefully grip firmly on all four corners of the mezzanine board to remove it from P8 and P9. Make sure all pins of the mezzanine's PL2 and P2 are aligned correctly before reinstalling the unit. The user should only have to access these option headers once to set up the user's initial application requirements.

J1 = CHN1

•

ē .

FANUC

- J2 = CHN2

- J3 = CHN3

Note: For two channel board J2 and J3 are dummy connectors.

#### 1.5.1 VME Access

Figure 1-4 shows the Memory Mode Configuration while Figure 1-5 shows the VME access configurations supported by the VME-4145.

Figure 1-4 VME Memory Mode Configuration

#### Figure 1-5 VME Access Mode Configuration

Supervisory

3 ● ●4 OR

Either Supervisory or Nonprivileged

Nonprivileged

#### 1.5.2 Base Address Jumpers

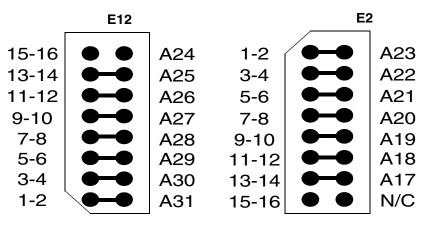

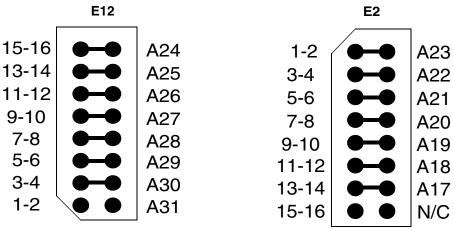

This set of jumpers is used to manually set the base address for the VME-4145 board. A jumper installed represents a logic 0, while a noninstalled jumper represents a logic 1. Figure 1-7 depicts the jumpers, E2 and E12, that are used to set the base address. Figure 1-7 and Figure 1-8 shows an example of how the base address jumpers represent the base address. In this example, the first 16 bits are hardwired to a logic 0.

Figure 1-7 Base Address Jumper Configuration

Example1: Base Address of 01000000

Figure 1-8 Example of Base Address Jumper Usage

**Example 2:** This Jumper Configuration Gives a Base Address of 0x80000000 when E26 and E27 are properly configured.

#### 1.5.3 Two-Channel Mezzanine Board

You can install an optional two-channel mezzanine board, Figure 1-2. This board contains the channel 2 and 3 DACs, engines, and waveform RAMs. The output of this circuitry is fed back down to the main board where the deglitcher, filters, and output buffer circuitry completes the output path. Install the two-channel optional mezzanine board onto P8 and P9 on the main board. See Figure 1-1 for the location of these connectors. Refer to Figure 1-2 for the usage of the jumpers located on the mezzanine board.

#### 1.5.4 Test Points

#### Table 1-3 Test Point Descriptions

| Test Point            | Description                               |  |  |

|-----------------------|-------------------------------------------|--|--|

| TP1                   | +5 VDC Voltage Reference                  |  |  |

| TP2                   | +2.5 VDC Voltage Reference                |  |  |

| TP3                   | DSP Flag Out Pin (FACTORY USE ONLY)       |  |  |

| TP4                   | +10 VDC Voltage Reference                 |  |  |

| TP5                   | Channel 0 END_ADDRESS* (FACTORY USE ONLY) |  |  |

| TP6                   | Channel 0 Last Cycle* (FACTORY USE ONLY)  |  |  |

| TP7                   | Channel 1 END_ADDRESS* (FACTORY USE ONLY) |  |  |

| TP8                   | Channel 1 Last Cycle* (FACTORY USE ONLY)  |  |  |

| Mezzanine Test Points |                                           |  |  |

| TP9                   | Channel 2 END_ADDRESS* (FACTORY USE ONLY) |  |  |

| TP10                  | Channel 2 Last Cycle* (FACTORY USE ONLY)  |  |  |

| TP11                  | Channel 3 END_ADDRESS* (FACTORY USE ONLY) |  |  |

| TP12                  | Channel 3 Last Cycle* (FACTORY USE ONLY)  |  |  |

#### **1.5.5 Potentiometers**

Potentiometers R13, R11, and R9 are located on the front panel of the VME-4145 board. The description of these potentiometers is given below in Table 1-4.

| Table 1-4 Potentiometer Descriptions |                                   |  |  |

|--------------------------------------|-----------------------------------|--|--|

| Potentiometer Description            |                                   |  |  |

| R13                                  | +2.5 VDC Voltage Reference Adjust |  |  |

| R11                                  | +5 VDC Voltage Reference Adjust   |  |  |

| R9                                   | +10 VDC Voltage Reference Adjust  |  |  |

#### **1.5.6 Fuses**

The VME-4145 uses one 10A axial wire lead fuse for the protection of the input of the DC-to-DC Converter.

#### 1.5.7 Headers

The board contains 0.1 inch headers. These are industry standard with numerous suppliers.

## **1.6 Calibration**

For maximum specified accuracy over time, the user must guarantee that the onboard voltage references remain precise. These references are used by the analog hardware and the DSP to calculate the gain and offset correction coefficients which are applied to the user's raw waveform data. Three precision references are used on the board: +2.5, +5, and +10 VDC.

#### **1.6.1 Test Equipment Required:**

- High accuracy and resolution Digital Voltmeter such as HP 3458A. The meter should display at least 6-1/2 digits or better and have a current NBS calibration.

- A small flat bladed screw driver or tuning tool (such as Hewlett-Packard Oscilloscope Probe tuning tool or jeweler's screw driver).

It is highly recommended that the test points on the board be used when monitoring and adjusting the potentiometers for reference voltages.

#### 1.6.2 +10.0 VDC Reference Voltage Calibration

Calibration Procedure:

- Monitor TP4 if you have a board extender to allow access to the side of the board.

- Analog ground return is at the GT1.

- If adjusting from the front panel, monitor the DB37, P3 pin 19.

- Analog ground return is DB37, P3 pin 37.

- Adjust front panel potentiometer R9 for +10.0000 VDC voltage reference.

The +5 V reference is dependent on the +10 V reference. Adjust +10 V first, then the +5 V. Check both test points (tp4 and tp1) after making the adjustments to ensure that the voltages are accurate.

#### 1.6.3 +5.0 VDC Reference Voltage Calibration

Calibration Procedure:

- Monitor TP1 if you have a board extender to allow access to the side of the board.

- Analog ground return is at the GT1.

- If adjusting from the front panel, monitor the DB37, P3 pin 18.

- Analog ground return is DB37, P3 pin 37.

- Adjust front panel potentiometer R11 for +5.0000VDC voltage reference.

#### 1.6.4 +2.5 VDC Reference Voltage Calibration

Calibration Procedure:

- Monitor TP2 if you have a board extender to allow access to the side of the board.

- Analog ground return is at the GT1.

- If adjusting from the front panel, monitor the DB37, P3 pin 17.

- Analog ground return is DB37, P3 pin 37.

- Adjust front panel potentiometer R13 for +2.50000VDC voltage reference.

## 2 • Theory of Operation

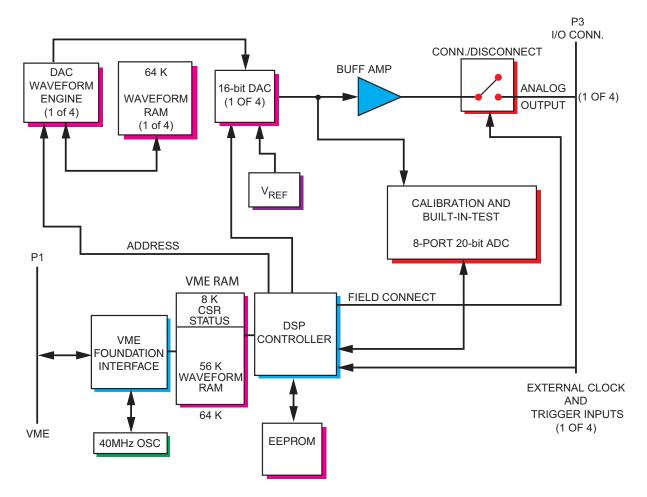

The VME-4145 provides four independent output channels. This capability is attained by the principal hardware functions, as shown in Figure 2-1 below. The VME-4145 contains the following principal functional elements:

- VME interface

- DSP

- EPROM/E2PROM

- DSP RAM and waveform RAM

- Control logic

- Timing and synchronization

- Analog output DACs

- Analog input ADC

Figure 2-1 VME-4145 Functional Block Diagram

## 2.1 General Operation

The following sections describe the process used to set up and operate the VME-4145.

There are three programmable operating modes available to the user:

- Continuous Mode Types I and II

- Single Cycle

- Continuous Burst

The sample clock source (internal or external) and period must also be programmed. The user can declare the use of an external trigger. The internal sample clocks are available at the front panel connector (P3). If the user has selected the Continuous Burst mode, the user must also set the idle time from one burst to the next burst. Both the sample clock and the buffer size can be programmed independently. Having a programmable buffer length allows the user the freedom from having to "fit" an integral number of waveform cycles in a fixed buffer size.

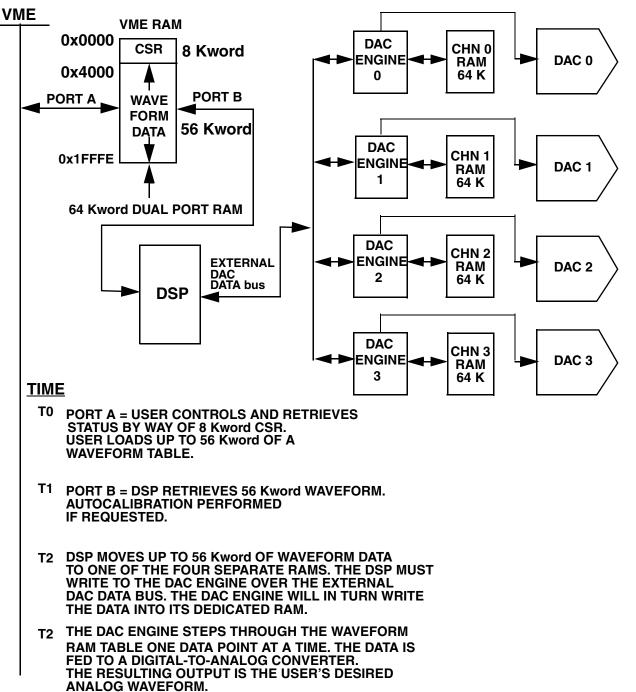

#### 2.1.1 VME-4145 Onboard RAM

There are four RAM memories and one Common VME Waveform Data RAM memory associated with the VME-4145 board. Each of the four channels has its own dedicated 64K x 16-bit of RAM. The user can load the waveform table into the Common VME Waveform Data RAM in 56 Kword of address space, beginning at address 0x4000 through 0x1FFFE. The other 8 Kword of RAM is used by the CSR. Figure 2-2 is an illustration of the VME-4145 RAM structure.

For each channel there is a dedicated DAC. The DAC receives its output data from a separate channel RAM (one per channel). The user sets the size of the input buffer and downloads the desired waveform data into the desired Waveform Data RAM (the upper 56 Kword). The DSP will manipulate this data, applying calibration corrections. During calibration, a table of offset and gain coefficients is compiled and stored in RAM. There is an entry for offset and gain corresponding to each of the four channels configured in each of the five output voltage ranges.

#### 2.1.2 Output Range

The VME-4145 generates bipolar and unipolar signals in the ranges stated in Table 2-1. The ranges are set up independently for each channel in the Channel Configuration register. Bipolar or unipolar signal outputs are jumper selectable.

| Table 2-1 Bipolar and Unipolar Voltage Ranges |        |  |  |  |  |

|-----------------------------------------------|--------|--|--|--|--|

| BIPOLAR and UNIPOLAR RANGES                   |        |  |  |  |  |

|                                               | 2.5VDC |  |  |  |  |

| BIPOLAR                                       | 5VDC   |  |  |  |  |

|                                               | 10VDC  |  |  |  |  |

| UNIPOLAR                                      | 5VDC   |  |  |  |  |

|                                               | 10VDC  |  |  |  |  |

Unipolar 0 to 2.5V is not supported.

#### 2.1.3 Data Engine Registers

Each channel has its own dedicated RAM and hardware control logic implemented in a large Erasable Programmable Logic Device (EPLD) that is called the "Data Engine," refer to Figure 2-1 on page 29. The Data Engine accesses the RAM to supply samples as needed to the DAC input register.

#### 2.1.4 Loading the Waveform Data Table

Waveform data is entered through a 64K x 16-bit waveform sample buffer. The buffer size is programmable from 2 to 65,536 samples per channel. The user configures a channel for either Continuous, Single Burst, or Continuous Types I and II Mode. The local DSP applies gain and offset corrections to the waveform samples, and stores them in the Channel RAM (not accessible by VME). Waveform generation begins with either a software trigger or an external trigger input. Each channel can use either an internal or external clock timebase input. During waveform generation, the trigger input is retriggerable and will restart an active waveform to the first location of the waveform table.

Each DAC, one per channel, has a 64K x 16-bit RAM Buffer. These buffers are not directly accessible to the user. The user must load the waveform table into the common Waveform Data RAM. The DSP will apply calibration offset and gain corrections to the data and transfer it to appropriate DAC engine's Channel RAM. The DSP accesses the Channel RAM through the DAC engine. Due to the Control and Status Register's overhead, the entire Common VME Waveform Data RAM is not available to the user for waveform downloading (8 Kword for the CSR and 56 Kword for the waveform data). Segmentation memory is allocated 2 Kword, starting at location 0x1000. If the user wishes to use segmented waveforms, the user must use a fixed starting address for that particular channel. Refer to Chapter 3, Programming. The download waveform data memory is allocated 56 Kword of memory space. For example, if the user requires the full 64 Kword for the waveform, they could load it in two parts: first, the 0 to 32 Kword part is loaded; and second, the load waveform command is issued. The user must poll the DSP for a command acknowledgment. This indicates the DSP has applied corrections and transferred the corrected data to the output buffer. The user then loads the 32 to 64 Kword portion and issues the second load memory command. The DSP will move Waveform Data RAM to DAC Engine Channel RAM based on

the VME start and end address pointers and DAC destination starting address pointers.

The channel's range and data format must be set before loading a waveform for that channel.

## 2.2 Modes of Operation

The three user-programmable operating modes are: Continuous Type I or II, Single Cycle, or Continuous Burst modes. These modes are described in the following sections and in the programming section of this manual.

#### 2.2.1 Continuous Modes Types I and II

In the Continuous Mode (Type I) of operation, the board will continually scan the waveform table and generate the desired signal until the board is halted. Therefore, once the waveform table reaches the end address, it resets the RAM address back to the first value and starts scanning through the data. In the Continuous Mode (Type II), the board scans the waveform table for a programmed number of (up to 510) cycles and then halts.

#### 2.2.2 Single Cycle Mode

In the Single Cycle mode of operation, the board scans through the waveform table and generates a waveform until the end address is reached. At that point, the waveform halts. The voltage of the last waveform sample is maintained at the output. If so desired, the user can set the last value to 0x0000 for unipolar or 0x8000 for bipolar signals. This will leave the output at 0.00 VDC.

#### 2.2.3 Continuous Burst Mode

In the Continuous Burst mode of operation, the board scans through the waveform table and generates a waveform until the **n**<sup>th</sup> value in the table is reached. Then the waveform stops. The voltage of the last waveform sample is maintained at the output. At this time, a secondary counter with a value 'IDLE Timer' (the value 'IDLE Timer' determines the number of master clock cycles to wait) is decremented toward zero. This secondary counter is decremented at the master clock rate of 40 MHz or 25 ns ticks. When the counter reaches zero, the RAM address counter resets the address back to the starting address value and resteps through the data.

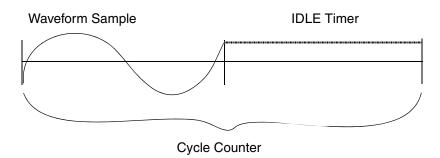

#### 2.3 Idle Timer

The IDLE Timer is used to place idle time between each time the board scans the waveform table. Once the output waveform table has reached its  $n^{th}$  value, a count down IDLE Delay Timer is activated. When the idle counter reaches zero, the address counter is once again reset to the first value in the waveform table and the waveform is output again.

The value of 'IDLE Timer' must be set by the user. The default value is zero.

The range of 'IDLE Timer' is:  $0 \le M \le 2^{24}$ -1 (25 ns Ticks).

If the value of 'IDLE Timer' = 0 is selected, the waveform is then generated repetitively with no delay.

#### 2.4 Cycle Counter

The Cycle Counter (P) determines the number of waveform cycles to generate. Once the waveform table has reached its waveform sample value, a cycle counter is decremented. Once this cycle counter has reached zero, waveform generation is halted for that channel. The cycle counter may be reprogrammed while a waveform is running. If the count was set to 511, the waveform would be running continually. If the user then sets the count to one, the waveform would run through the waveform table for the last time and then stop. This is one way to **halt** the waveform and allow it to be retriggered at a later time. Do not set the count to zero while a waveform is running; the hardware will not operate correctly.

The value of the 'Cycle Counter' must be set by the user. The default value is 511 cycles.

The programming range of the 'P' is:  $1 \le P \le 511$  (0x1FF), with 'P' representing the Cycle Counter.

If the value of P = 511 is selected, then an infinite number of cycles are generated. This is used to select the continuous mode (Type I) and continuous burst modes (Type II).

#### 2.4.1 Examples of Setting Up Modes

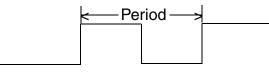

Table 2-2 and Figure 2-3 on page 34 provides examples of different ways the user can set up the board to operate in one of the three modes using the IDLE Timer and Cycle Counter registers.

#### Figure 2-3 Example of the Burst Mode Type I

#### Table 2-2 Example Settings: Modes

| Mode               | Description                                                 | Waveform Sample<br>Counter | IDLE<br>Timer | Cycle<br>Counter |

|--------------------|-------------------------------------------------------------|----------------------------|---------------|------------------|

| Туре I             | Continuous                                                  | >2                         | 0             | 511              |

| Type II            | Run for N cycles and stop                                   | >2                         | 0             | 254              |

| Single Cycle       | One burst and stop                                          | >2                         | 0             | 1                |

| Burst IDLE Type I  | Burst then wait 1,000 clocks for<br>5 cycles and then stop  | >2                         | 1,000         | 5                |

| Burst IDLE Type II | Burst then wait 1,000 clocks,<br>then repeated indefinitely | >2                         | 1,000         | 511              |

#### 2.5 Sample Clock and Trigger

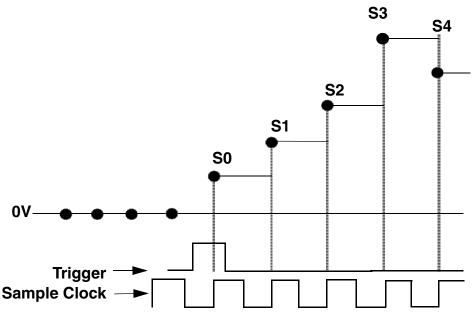

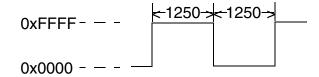

The Sample Clock (on its rising edge) causes a read of the next output data value from the Waveform Data RAM and outputs to the DAC. The sample clock source (internal or external) and period must be programmed by the user. Each channel has its own dedicated clock source. This dedicated clock source allows the generation of four waveforms at different frequencies. Figure 2-4 on page 36 shows the sample clock and waveform output relationship. The trigger input is used to start a waveform output. The user may select to enable the external trigger function or use an internal software trigger.

The internal sample clock is a free running continuous clock. The clock can also be controlled from software and it can be programmed to a static logic one or zero. In this way, the software can generate ultralong period waveforms. Finally, each channel may select a common clock allowing two or more channels to have synchronized outputs. Channel zero's sample clock is the source of the common clock. The trigger input can be used to synchronize the output waveform with some external event. Please note that in Figure 2-4, the example shows the user has selected the external trigger mode. The waveform will not begin until the trigger has occurred.

#### 2.5.1 Internal Sample Clock

The maximum frequency of operation for the DACs is 2.5 MHz or 2.5 Million samples per second (Msps). This corresponds to a minimum period of 400ns per sample. The incremental step size is 25 ns from a 40 MHz master oscillator. The 20-bit Sample Rate registers (SR3-SR0) are set for the number of 25 ns clock cycles to wait per sample output. Both the sample clock and the buffer size can be programmed independently. Having a programmable buffer length frees the user from having to 'fit' an integral number of waveform cycles in a fixed buffer size. The sample clocks may be changed while a waveform is running.

#### **Internal Sample Clock Specification:**

400 ns to 26.6 ms (with 25 ns resolution). (SR3-SR0) = 0X00010 to 0XFFFFF

Trigger: Starts burst waveform generation

Sample Clock: New data sample every rising edge of clock (after trigger)

S0, S1, S2, S3, S4,.....Sn-1, Sn: Waveform Samples. Programmed using WSB.

Ts: Sample period. Programmed using SRx.

#### 2.5.2 External Sample Clock

Each channel has an external input for a user-supplied sample clock. If the user decides on using the external clock instead of the internal clock, the external clock must be guaranteed within its clock specifications of voltage, period, and duty cycle. The programming is discussed in Chapter 3, Programming. Also refer to, Front Panel Signal Buffers, for a detailed explanation of the front panel signal buffers.

#### **External Sample Clock Specification:**

- **Period:** 400 ns period (minimum)

- Clock Pulse Width: >120 ns

- **Voltage:** CMOS TTL compatible (Low <0.8 VDC, High >3.15 VDC)

#### NOTE

It is recommended that the user use the internal clock while setting up the engine and downloading a waveform. Once this is done, the user can switch to the external clock to output the waveform.

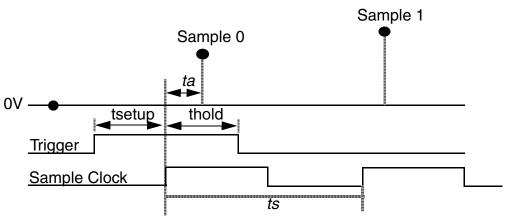

#### 2.5.3 External Trigger

Each channel has an external input for a user-supplied trigger. If the user decides on using an external trigger instead of a software trigger, the user must guarantee this trigger is within the specifications of voltage and period. It must also meet the setup and hold times specified. See Figure 2-5 for details.

- **Voltage:** CMOS TTL Compatible (Low <0.8 VDC, High >3.15 VDC)

- tp Trigger Period: 500 ns period (minimum)

- **ts Setup Time:** >50 ns

- th Hold Time: >100 ns

- **Trigger Latency:** 300 ns

- ta Clock edge to Analog value change: 200 ns (maximum)

Figure 2-5 External Trigger

- **tsetup:** Setup time before rising edge of sample clock.

- **thold:** Hold time after rising edge of sample clock.

- **tp:** Minimum pulse width for trigger pulse.

- Sample Clock: New data sample every rising edge of clock (after trigger).

- S0,S1,...Sn-1, Sn: Waveform Samples. Programmed using WSB.

- Ts: Sample period. Programmed using SRx.

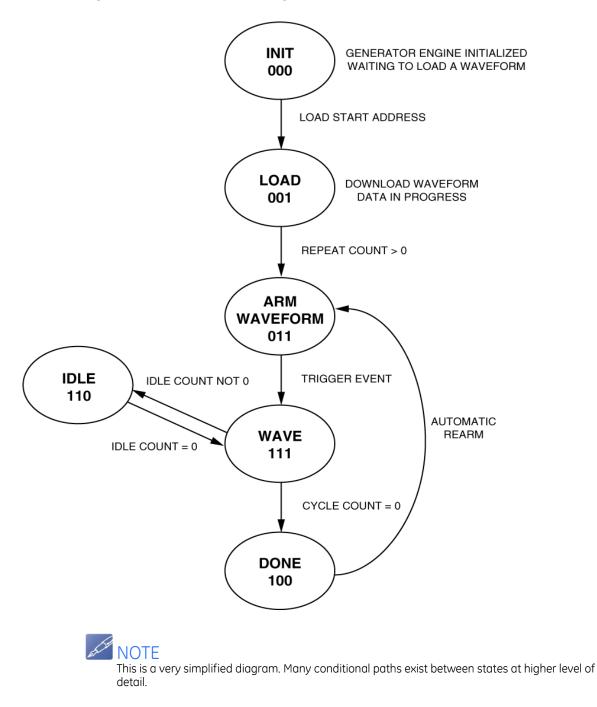

# 2.6 Hardware States

The channel's control hardware has six operating states: INIT, LOAD, ARM, WAVE, IDLE, and DONE states.

In the *LOAD* state, the board is ready to load a waveform. The user loads the waveform table, and can elect to take all channels offline. The user also elects to leave the DAC at the last table value it generated.

In the *ARM* state, the board is waiting for a software trigger or an externally supplied trigger. Once the board is "triggered," the state becomes WAVE and the first waveform RAM buffer value is read and sent to the DAC.

In the *WAVE* state, the board is actively reading from the RAM and writing to the DAC at the sample clock frequency. When P = 511, the WAVE state is never exited until a user software HALT command is given. When P<511, the board will run until the desired number of waveform cycles has been generated. Then the board enters either the ARM or DONE state.

In the *IDLE* state, the board is holding at the last value in the table.

In the *DONE* state, the board will automatically enter the ARM state. The **DONE** state is transitioned through faster than the DSP can capture. Therefore, the user should not attempt to monitor for this state. Once a waveform halts, it will automatically rearm and wait for a new trigger.

The user enters a particular channel into the DONE state by issuing the channel HALT command. This leaves the DAC output value at the last value written.

# 2.7 VME Interface

The VME-4145 responds to word (D16) or byte (D08) data accesses. Supervisory, nonprivileged, or both access modes are supported along with extended and standard address modes.

## 2.8 Commands

The user can issue a number of commands to the VME-4145 by way of the VME. The commands are initiated by the VME byte write access to the indicated address. The section in Chapter 3 titled *VME-4145 Commands* discusses the various commands that can be issued through the Control Registers along with the required parameters and the expected responses.

### 2.9 Calibration

The initiate calibration command causes the board to stop processing data, enter the calibration mode, and blink the front panel LED. Any VME read accesses during the calibration period will return a value of 0x3C00. All VME writes will be ignored.

The DSP utilizes the 20-bit Sigma-Delta ADC to read each of the output channels at various output values from 0x0000 to 0xFFFF. First, the ADC is self-calibrated. The ADC's programmable attenuator is then analyzed for gain and offset errors using the onboard 2.5, 5, and 10 V precision references. Gain and offset correction factors are then calculated. Finally, each DAC channel is analyzed for all ranges supported by the current unipolar/bipolar hardware strap.

Once the DSP recognizes a user calibration request, there are a number of calculations the DSP will process. Therefore, during this time interval, the VME-4145 will be busy and not able to generate any waveforms or respond to other commands. A large number of samples are taken for each ADC reading. These multiple readings per data point are averaged to reduce noise-related errors. Finally, all of the data points are analyzed and a "Least Square Statistical Algorithm" is applied to determine the gain and offset coefficients. Typically, the DSP will be busy for over 10 to 20 minutes of processing time.

When autocalibration is initiated by a software command, an embedded DSP loads calibration values into each of the output DACs. The output voltages are read back into the DSP through a 20-bit Sigma-Delta ADC. This is repeated until a sufficient number of calibration points have been measured. A calibration table consisting of offset and gain corrections for each of the four outputs in each of the voltage ranges is compiled and stored in RAM. These correction factors are used to correct the data when the waveform sample buffer is loaded.

Due to the lengthy calibration time, the unit is not automatically calibrated at each power on cycle of the board. However, once the board has been calibrated, the stored coefficients may be recalled for reuse.

As a first step, the ADC is given a self-calibrate command. The 20-bit ADC will autocalibrate itself by grounding its own input and reading the external voltage reference.

After the ADC is calibrated, the programmable attenuator in front of the ADC is analyzed to determine its offset and gain errors using the onboard precision 2.5, 5, and 10 VDC references.

It is important that the user guarantee the accuracy of these references since they are the basis of all calibration for the board.

Now that the ADC and its input attenuator are both calibrated, the DSP can analyze each of the DAC channels to determine their independent gain and offset coefficients.

Please note that the unit may only calculate DAC coefficients depending on how each channel is configured prior to the calibration request. Due to a manual user hardware strap option that determines whether the DAC is a bipolar or unipolar output, the DSP will only calibrate for that configuration. For example, if the user has a channel set for unipolar output, only the 0 to +10 and 0 to +5 VDC coefficients will be determined. Likewise, if the user has a channel set for bipolar output, only the  $\pm 2.5, \pm 5$ , and  $\pm 10$  VDC coefficients will be determined. If the user changes this hardware strap, the user should recalibrate the board for the new ranges. The DSP cannot read these unipolar/bipolar straps directly. The user must inform the DSP through the Channel Configuration Registers (CCRs) using Bit 12. It is important that the user set all four of the CCRs prior to invoking calibration. This will inform the DSP which coefficients it should calculate (bipolar or unipolar).

After calibration has completed, the new calibration coefficients will remain in volatile RAM. They will remain usable until the board's power has been removed. If the user wishes to retain these values permanently in  $E^2$ PROM, the user must issue the upload RAM coefficients to  $E^2$ PROM command. The user may upload to  $E^2$ PROM 10,000 times. The data will be retained for at least ten years. If the 10,000 time limit is exceeded, the socketed PLCC  $E^2$ PROM device will need to be replaced.

The user has two options once the VME-4145 is powered up. With the first option, the user may issue a calibration command and wait for autocalibration to finish. This method is suggested for users requiring high accuracy DC values or where there are extreme temperature variations. This method will, of course, require the VME-4145 to remain busy for a period after powerup. The second option is to issue a download E<sup>2</sup>PROM coefficients to RAM command. The previously determined coefficients are retrieved from permanent storage and moved into the working volatile RAM memory of the DSP. If the user is more interested in AC waveforms, then this method will be attractive since it is the faster of the two.

# 2.10 Digital Signal Processor (DSP)

The DSP is responsible for gathering calibration data from the ADC and providing offset and gain correction to the user's waveform data. The DSP and EPLD combine to control all board operations. A **least means square** approximation of the channel transfer function is determined using this data.

The gain and offset coefficient for each channel are calculated from this estimate and stored internally. When calibration is complete, the DSP sets a bit to inform the user of calibration completion.

After the user loads a new waveform, the DSP applies the gain and offset calibration coefficients. Calibration is performed sample-by-sample as it is moved from the VME RAM to DAC RAM.

# 2.11 EPROM

The DSP firmware is stored in the EPROM. There are four main boot pages stored in the EPROM: the power up/reset boot page, main routine boot page, calibration boot page, and the reconfiguration boot page.

# 2.12 E<sup>2</sup>PROM

The gain and offset coefficients calculated in the Calibration mode are stored in the E<sup>2</sup>PROM. The board is shipped with factory-determined bipolar coefficients. When the user initiates calibration, newly calculated coefficients are stored in the DSP for use in real-time correction. The new coefficients are not automatically stored in the E<sup>2</sup>PROM. A command must be issued to upload the new coefficients to the E<sup>2</sup>PROM for permanent storage. This allows the user to run new correction coefficients that are not stored in the E<sup>2</sup>PROM. Most commercially available E<sup>2</sup>PROMs have a guaranteed 10,000 write cycle lifetime. A E<sup>2</sup>PROM Writes Register (EWR) is available to the user indicating how many writes have occurred. If this number gets close to 10,000 limit, it is suggested that the E<sup>2</sup>PROM be replaced so data is not lost or corrupted. The E<sup>2</sup>PROM also contains 12 Kword of data which configures the DAC Data Engines on power up. The user does not have direct access to this memory.

# 2.13 Control Logic

The control logic consists of the logic required to read and write the RAM and  $E^2$ PROM, as well as, load and initiate waveform generation and arbitration between the board and the VME. The control logic consists of an EPLD.

# 2.14 Analog Circuitry

The digital data from each waveform buffer is fed to a DAC. The range options are handled at this point as well. The range adjust output is fed to a track-and-hold deglitcher. The track-and-hold output is then routed to an optional low pass filter circuit. The output of the filter is routed to a high-current driver Op-Amp capable of driving high capacitance loads. An analog switch is included to disconnect the output from field wiring. This allows the board to test the DAC without affecting external devices. A 20-bit ADC is used to calculate calibration parameters for the DAC.

### 2.14.1 Digital-to-Analog Converter (DAC)

The DAC is a monolithic high-performance device which accepts 16 bits of digital data and converts it into an analog representation. The current output of the DAC is routed into a current to voltage conversion Op-Amp. The voltage output of the Op-Amp is fed into track-and-hold circuitry. This reduces output glitches which can occur during DAC conversions.

### 2.14.2 Analog-to-Digital Converter (ADC)

The ADC uses a Sigma-Delta conversion technique to digitize input signals with up to 20 bits of no missing code performance. There is one ADC on the board; its input utilizes an analog multiplexer to select one of the four channels. In front of the ADC is a programmable attenuator. This provides the nominal 2.5VDC magnitude input range of the ADC. The ADC is controlled by the DSP.

### 2.14.3 Analog Output Filtering (Optional)

Each channel can be routed through a four-pole Salen-Key filter. For applications requiring low pass filters, GE Fanuc Intelligent Platforms provides optional Filters assembled per channel. All filters are Fourth-Order, Salen-Key Multiple Feedback Low Pass Filters. Check Table 2-3 below for currently available filters and cutoff frequencies.

| FILTER       | TYPE      | CUT OFF FREQUENCY              |  |

|--------------|-----------|--------------------------------|--|

| VME-4145-10x | Chebyshev | 500 kHz                        |  |

| VME-4145-20x | Chebyshev | 1.0 MHz                        |  |

| VME-4145-30x | Bessel    | 500 kHz                        |  |

| VME-4145-40x | Bessel    | 1.0 MHz                        |  |